Enabling 5G Data Communication

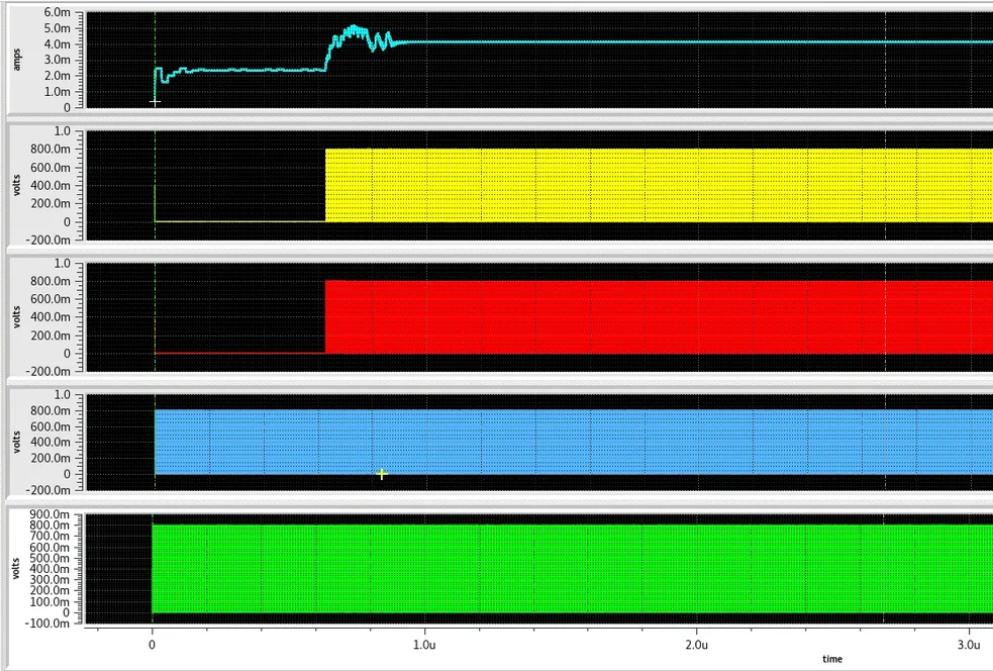

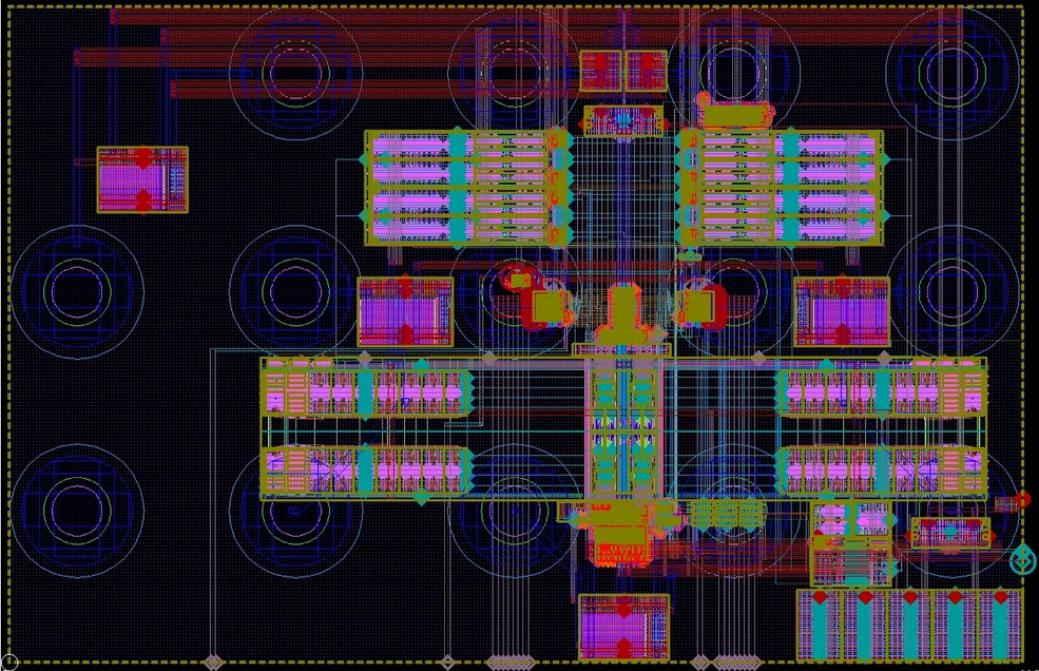

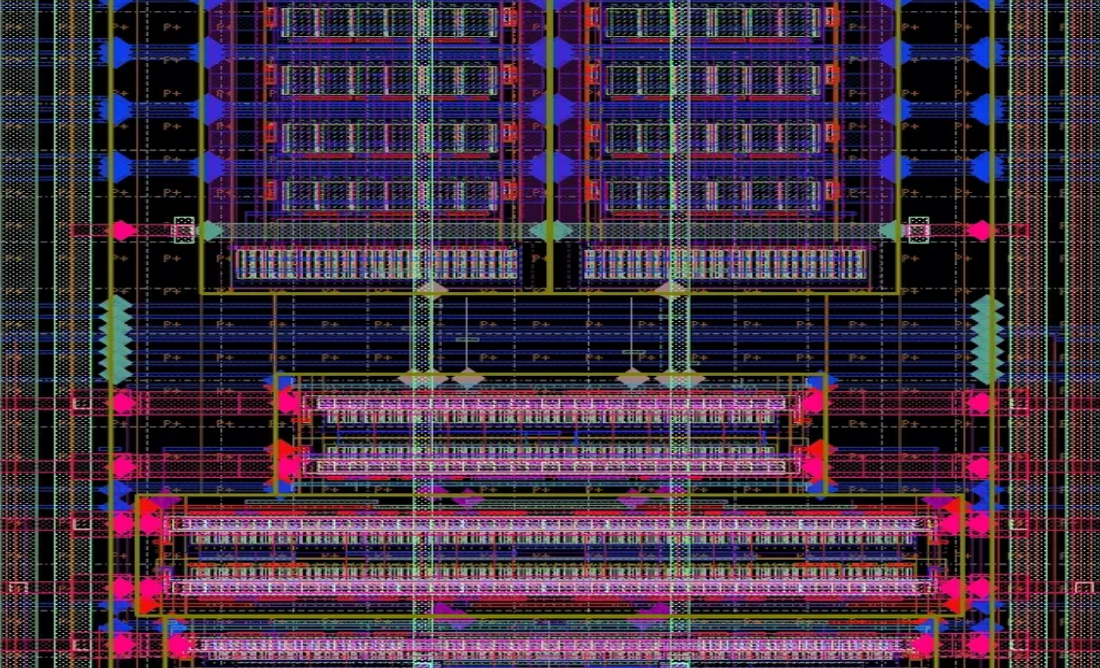

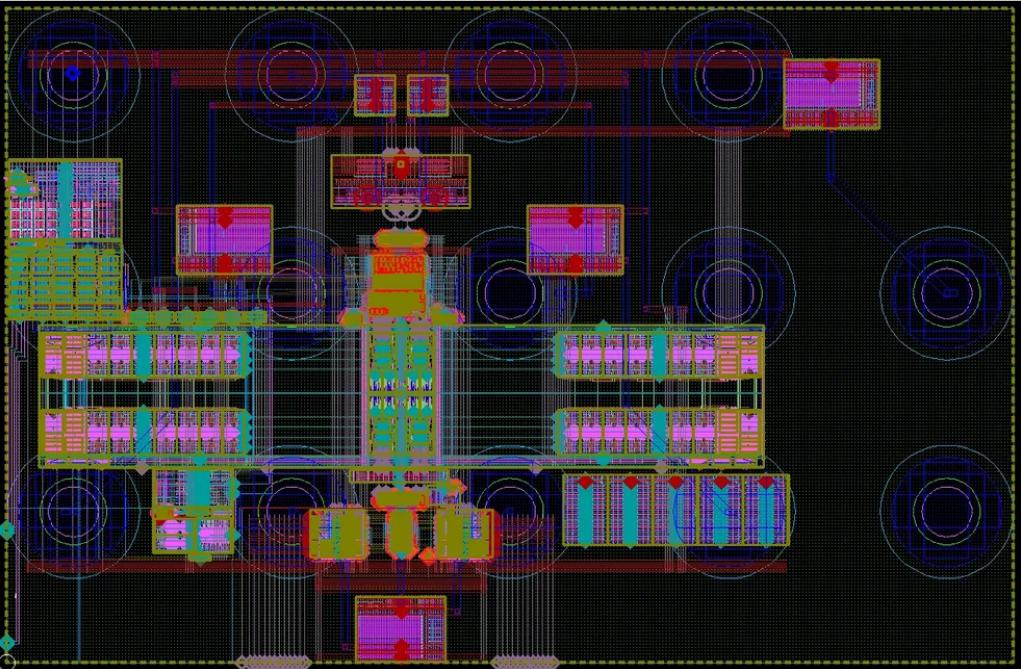

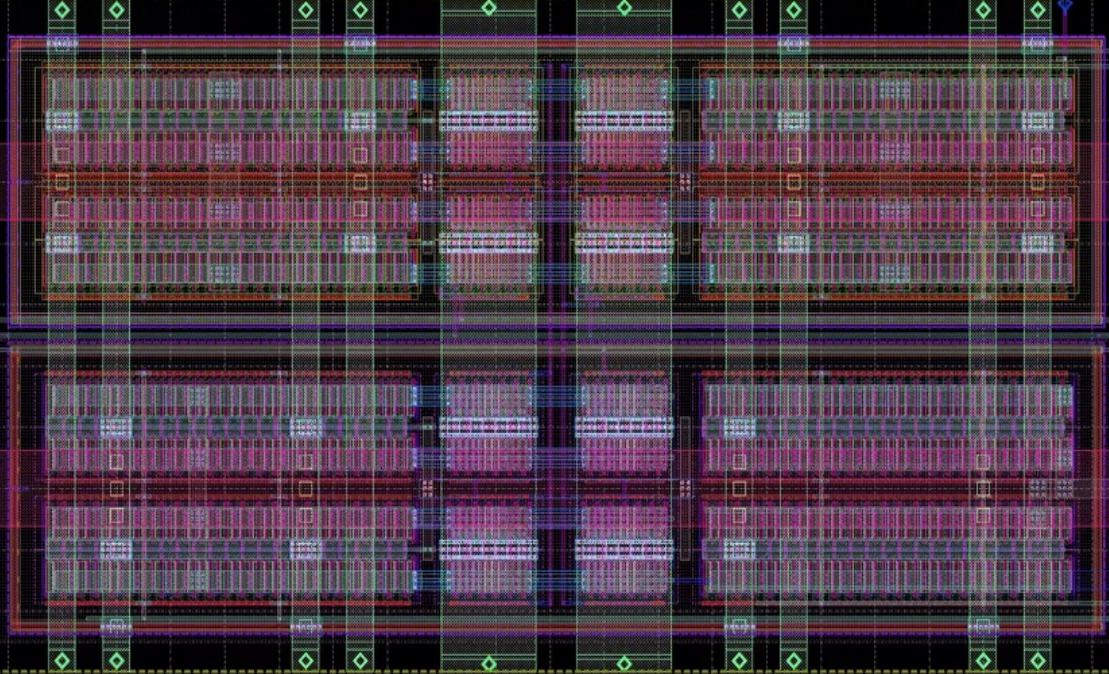

Western Semiconductor’s SerDes IP is an NRZ embedded clock system proven in silicon from 65nm to 12nm with speeds ranging from 10.313 to 56Gbps. All of our SerDes cores are based on trusted ring PLLs to match a vast range of industry needs, while our library of +130 standard cells allows us to rapidly customize special-purpose SerDes technology for high-performance applications.

For a more thorough discussion on our NRZ single channel SerDes, please see our SerDes Interfaces data sheet, downloadable in PDF format.

Further Information

Western Semiconductor provides an extensive list of trusted silicon IP. Please contact us for a detailed report on our SerDes technology.

Key Features

- NRZ system with embedded clock architecture

- Programmable 8bit and 16bit Serialization

- Deserialization available in 12m to 65nm

- PCI Express and FIFO protocols available

- Analog 8bit CDR with LVDS

- CML input and output drivers

- PISO, PIPO, SIPO, and SISO components tested and proven in silicon down to 12nm

- Guaranteed signal integrity with extremely low jitter of < 0.3 Ul

- Consistent jitter tolerance in harsh mixed-signal environments